Microchip Announces Flashtec NVMe 3108 PCIe 4.0 Enterprise SSD Controller

by Billy Tallis on August 4, 2020 8:00 AM EST

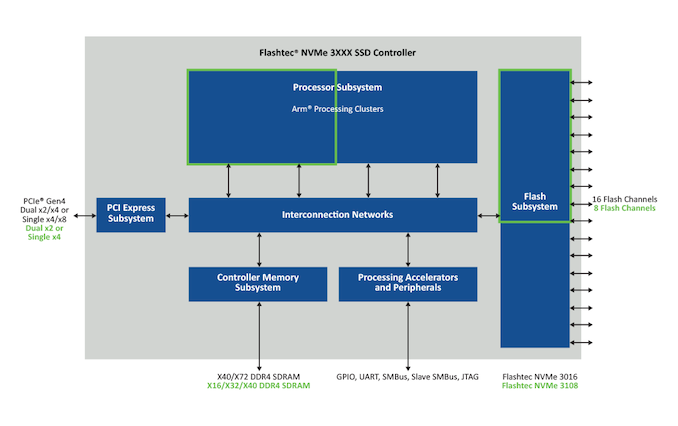

Microchip is announcing their first PCIe 4.0-capable SSD controller for low-power and entry-level enterprise SSDs. The new Flashtec NVMe 3108 is the smaller 8-channel derivative of the 16-channel Flashtec 3016, first announced two years ago. The 3016 has since moved from sampling to mass production, and as a derivative based on the same architecture, the new 3108 is expected to make that same transition much more quickly: sampling now, and production sometime in the first half of next year.

The Flashtec NVMe 3108 isn't quite literally a 3016 sliced in half, but that was more or less the starting point for developing the 3108. In discussing how the 3016 and 3108 differ, Microchip opened up a bit more about their controller architecture in general, and how their PCIe 4.0 generation 3xxx controllers are different from the earlier PCI 3.0 based Flashtec NVMe 2xxx controllers. First and least surprising, both the 3016 and 3108 are built on a 16nm FinFET process, which is what almost all PCIe 4.0 SSD controllers are adopting.

The external IO interfaces of the Flashtec NVMe 3108 are mostly cut in half relative to the NVMe 3016: 4 rather than 8 lanes of PCIe, 8 rather than 16 channels for interfacing with the NAND flash. The DDR4 DRAM interface on the 3108 can operate as a 16-bit, 32-bit or 40-bit (32+8 bit ECC) bus, while the 3016 uses either a 40-bit (32+8) or 72-bit (64+8) bus width. All together, these changes lead to a drastically lowered pin count, allowing the 3108 controller to use a package small enough to fit on a M.2 SSD. There's also some significant die space and power savings.

The 3108 runs its DDR4 interface a bit slower than its larger sibling (2400 MHz instead of 3200 MHz), but supports the same NAND interface speeds up to 1200 MT/s — a huge improvement over the 533 MT/s supported by the previous generation Flashtec controllers. This allows the 3108 to hit sequential read speeds of over 6 GB/s and random read speeds of 1M IOPS when paired with sufficiently fast flash memory. This isn't quite saturating what a PCIe 4 x4 link is capable of, but is competitive with other PCIe gen4 enterprise SSD solutions that have been announced such as the Samsung PM9A3 (6.5GB/s, 900k IOPS) or the 16-channel Kioxia CD6 (6.2GB/s, 1M IOPS).

The Flashtec NVMe 3108 includes fewer processor cores than the 3016, but still more than necessary for implementing basic SSD functionality. Microchip has designed the 3108 and the 3016 with spare processing power to accommodate computational storage use cases. This generation switched from Tensilica CPU cores to Arm cores, making for a more familiar development environment for customers developing firmware for these SSD controllers. Microchip says some customers are even running Linux on a subset of the controller's Arm cores.

Two major features of the Flashtec NVMe 3016 are outright missing on the 3108. The smaller controller doesn't include the compression accelerator hardware from the 3016, so it is not as well suited for computational storage duty along those lines. The 3108 also lacks the expansion port of the 3016. The larger chip's expansion port is intended to allow two SSD controllers to pair up and be used as a 32-channel controller, since Microchip is no longer producing a monolithic 32-channel version of their controllers. This expansion port is unneeded on the 3108 since they already have a 16-channel solution that is simpler and likely faster and more efficient than a dual-chip 8+8 channel setup would be. (Competitors in the enterprise SSD controller space have also used dual-controller designs, such as Marvell's dual-chip 16-channel solution. Silicon Motion has taken an in-between strategy, designing a single-chip 16-channel controller that is internally organized much like a combination of two 8-channel controllers.)

Aside from those features, the 3108 checks all the same boxes as the 3016: support for cryptographically verified firmware, dual-port PCIe, virtualization. Customers building SSDs with the 3108 should be able to implement the full range of NVMe 1.4 features and probably anything coming in NVMe 2.0, though not everyone will be including all of those optional features in their firmware.

Microchip's customers for Flashtec SSD controllers include numerous SSD vendors as well as some hyperscale cloud service providers who design their own SSDs. Each of these has their own firmware development and QA processes and few are particularly open about their long-term roadmaps, so it's hard to say when we'll start seeing final products using the new Flashtec NVMe 3108 controller. Most of our hands-on experience with Flashtec SSD controllers has come from Memblaze's PBlaze5 family, which was jointly developed with Micron and related to their 9xxx series SSDs. Memblaze just announced new models using the 2108 controller, so their 3108-based drives are probably over a year away.

Source: Microchip

5 Comments

View All Comments

Tomatotech - Wednesday, August 5, 2020 - link

NVMe 2.0? This is the first I've heard of it. A quick google search reveals a very few mentions of it, but no summaries or any concrete info about what's proposed. Anyone know more?Billy Tallis - Wednesday, August 5, 2020 - link

The main reason why they're jumping to 2.0 instead of calling it 1.5 is that they're reorganizing the spec to be more modular. There will be a base spec, separate specs for each command set (block IO, zoned, key-value), and separate specs for each transport (PCIe, RDMA, TCP). Aside from that reorganization, in terms of new functionality 2.0 won't be much larger than usual. So far, they've ratified and published 8 Technical Proposals defining new functionality on top of 1.4.Tomatotech - Thursday, August 6, 2020 - link

I see you've now written more about some NVMe 2.0 proposals. Thanks!https://www.anandtech.com/show/15959/nvme-zoned-na...

Tomatotech - Wednesday, August 5, 2020 - link

2021: Your storage gumstick runs an embedded ARM CPU that is powerful enough to run Linux decently well in its own right, sending data to your ARM main CPU via the ARM secure encryption chip on your Apple laptop, pulling data from an ARM-equipped datacentre, while you talk on your ARM CPU powered high-spec phone, driving your car stuffed full of ARM chips, while munching on a sandwich from your ARM-embedded toaster as your ARM-chipped fridge orders more cheese for tomorrow.Luckz - Sunday, September 6, 2020 - link

So much vertical integration will surely cost customers an ARM and a leg.