The Intel Lakefield Deep Dive: Everything To Know About the First x86 Hybrid CPU

by Dr. Ian Cutress on July 2, 2020 9:00 AM ESTLakefield in Terms of Laptop Size

In a traditional AMD or Intel processor designed for laptops, we experience two to eight processing cores, along with some graphics performance, and it is up to the company to build the chip with the aim of hitting the right efficiency point (15 W, or 35/45 W) to enable the best performance for a given power window. These processors also contain a lot of extra connectivity and functionality, such as a dual channel memory controller, extra PCIe lanes to support external graphics, support for USB port connectivity or an external connectivity hub, or in the case of Intel’s latest designs, support for Thunderbolt built right into the silicon without the need for an external controller. These processors typically have physical dimensions of 150 square millimeters or more, and in a notebook, when paired with the additional power delivery and controllers needed such as Wi-Fi and modems, can tend towards the board inside the system (the motherboard) totaling 15 square inches total.

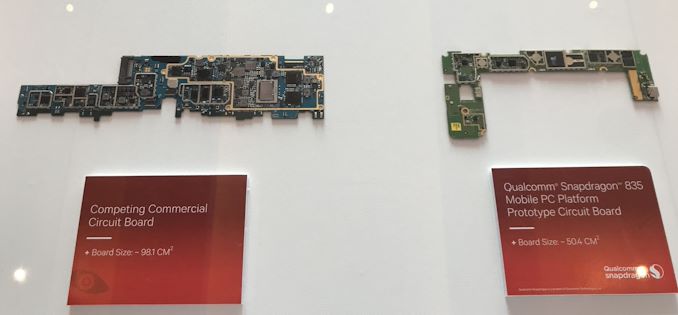

One of Qualcomm’s examples from 2018

For a Qualcomm processor designed for laptops, the silicon is a paired down to the essentials commonly associated with a smartphone. This means that modem connectivity is built into the processor, and the hardware associated with power delivery and USB are all on the scale of a smartphone. This means a motherboard designed around a Qualcomm processor will be around half the size, enabling different form factors, or more battery capacity in the same size laptop chassis.

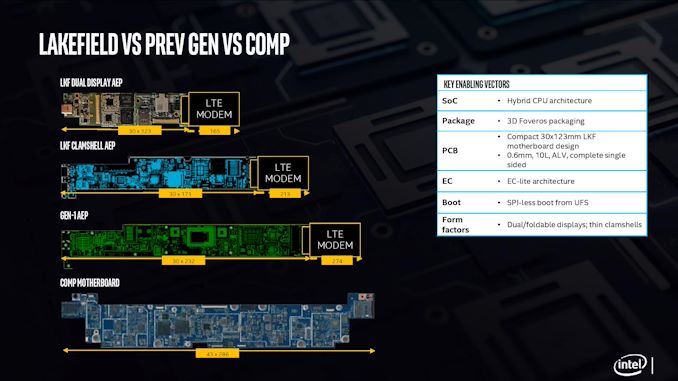

With Intel’s new Lakefield processor design, the chip is a lot smaller than previous Intel implementations. The company designed the processor from the ground up, with as much included on the CPU as to not need additional chips on the motherboard, and to fit the dimensions similar to one of Qualcomm’s processors. Above is a slide showing how Intel believes that with an LTE modem included, a Lakefield motherboard can move down to 7.7 square inches, similar to a Qualcomm design. This leaves more room for battery inside a device.

When Intel compares it against its own previous low power CPU implementations, the company quotes a 60% decrease in overall board area compared to its first generation 4.5 W processors.

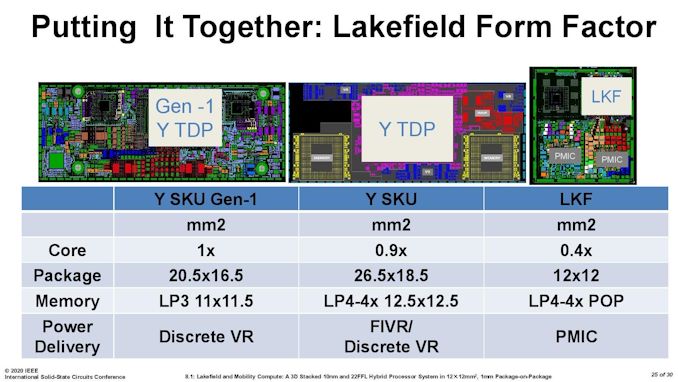

It is worth noting that for power delivery, Intel placed MIMCAPs inside the Lakefield silicon, much like a smartphone processor, and as a result it can get by on the power delivery implementation with a pair of PMICs (power management ICs). The reason why there is two is because of the two silicon dies inside – they are controlled differently for power for a number of technical reasons. If each layer within an active stacked implementation requires its own PMIC, that would presumably put an upper limit on future stacked designs – I fully expect Intel to be working on some sort of solution for this for it not to be an issue, however that wasn’t implemented in time for Lakefield.

For those that are interested, Lakefield’s PMICs are under the codenames Warren Cove and Castro Cover, and were developed in 2017-2018.

221 Comments

View All Comments

yeeeeman - Friday, July 3, 2020 - link

The successor (Gracemont) comes next year in Alder Lake S. Stop being a hater and go eat your amd cake.anonomouse - Thursday, July 2, 2020 - link

There are bigger challenges for asymmetric core design beyond just the actual ISA support and scheduling, too. Multithreaded software has lots of assumptions around locks and spinlocks in particular that will have to be tuned, and effective priority inversions will be problematic too. Like where a thread on the big core has to wait on a lock that is held by a thread running on a small core.Notebookcheck's article made it seem like the scheduling right now just doesn't sustain using all of the Tremonts + the Sunny Cove at the same time, which neatly sort of sidesteps the issue for now, at obvious cost of the perf of that bigger core. Not clear whether that's intended behavior that will stick around.

wr3zzz - Thursday, July 2, 2020 - link

There is no need for so many little cores if software were not designed to continuously phone home with our personal data, or skimming money continuously via micro-transactions. The entire ecosystem of phones is designed around that concept. PC, not so much, for now.jeremyshaw - Thursday, July 2, 2020 - link

Too late. MSFT and Intel are pushing that rehashed garbage "Modern Standby" (formerly Connected Standby, InstantGo, etc), which is trying to make laptops that don't go into standby - rather they go into a low idle state and "perform tasks" throughout the night.Usually, it just drains the battery on my laptop (I have long disabled automatic mail retrieval, and any other scheduled task) and forces the laptop into hibernate. Just what I want out of my laptop - less battery life.

Luckily for us, AMD laptops don't support this garbage fire.

MSFT... just because Apple was able to successfully implement "Modern Standby" almost a decade ago, doesn't mean you can. Wake up. Or not.

abufrejoval - Friday, July 3, 2020 - link

Yeah, had to laptop batteries killed because they woke up in the middle of a flight packed tight and overheating. Hybrid and modern standby are absolute "killer features".brantron - Thursday, July 2, 2020 - link

Why not two tiny Cannon Lake cores?I'm no Intel engineer, but the inconvenient fact remains that such a device would be more useful to the average person.

That leaves Lakefield with the appearance of a frankenstein experiment. Sorry Intel, sounds fun, but I don't buy those for $1,000+.

serendip - Thursday, July 2, 2020 - link

This is the most damning quote from the article:"Intel has made the 1+4 design to act as a 0+4 design that sometimes has access to a higher performance mode. Whereas smartphone chips are designed for all eight cores to power on for sustained periods, Lakefield is built only for 0+4 sustained workloads. And that might ultimately be its downfall."

And this is going into $1000 devices like the Galaxy Book S and Thinkpad Fold. The ARM 8cx variant of the Galaxy Book S is $999, the Surface Pro X with an upgraded 8cx is also $999, and these offer i5 level performance when running ARM code. They also have surprisingly beefy integrated GPUs.

Now imagine paying $999 for a 4-core Atom device with a Sunny Cove core that mostly sits idle. I've used cheap Bay Trail and Apollo Lake Atoms, they're decent performers at low price points but they don't belong in anything over $500 because they're still laggy.

I've also compared the Pentium 4415Y vs. the m3-8100Y in the old and new Surface Go: the Kaby Lake Pentium dual-core feels slightly laggy because it can't turbo, whereas the m3 feels much more snappy when it turbos. Even then, the Pentium still feels more snappy than Apollo Lake because single-core performance is higher. For daily use, Windows likes fat beefy cores with high turbo because a lot of the UI is single-threaded.

brantron - Friday, July 3, 2020 - link

And in addition to the m3's turbo, there's hyper-threading and AVX to account for.What clock speed would Ice Lake Y or Tiger Lake Y have with no hyper-threading or AVX?

Something doesn't add up here, and it's not just the bizarre hybrid cores.

serendip - Friday, July 3, 2020 - link

Yes, the m3 has HT and so does the much maligned Pentium Gold 4415Y and 4425Y.Lakefield looks fascinating from purely technical viewpoint but from a value standpoint, it looks to be a disaster. Intel actually thinks 4 Tremont Atom cores are going to be the main cores for $1000 devices.

Meteor2 - Friday, July 3, 2020 - link

Think of the margins though