The Intel Lakefield Deep Dive: Everything To Know About the First x86 Hybrid CPU

by Dr. Ian Cutress on July 2, 2020 9:00 AM ESTHow To Treat a 1+4 Hybrid CPU

At the top of the article, I explained that the reason for using two different types of processor core, one big on performance and the other big on efficiency, was that users could get the best of both worlds depending on if a workload could be run efficiently in the background, or needed the high performance for a user experience interaction. You may have caught onto the fact that I also stated that because Intel is using a 1+4 design, it actually makes more sense for multi-threaded workloads to run on the four Atom cores.

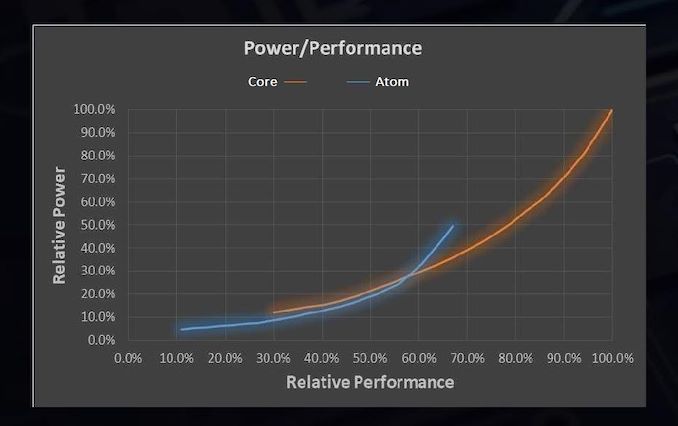

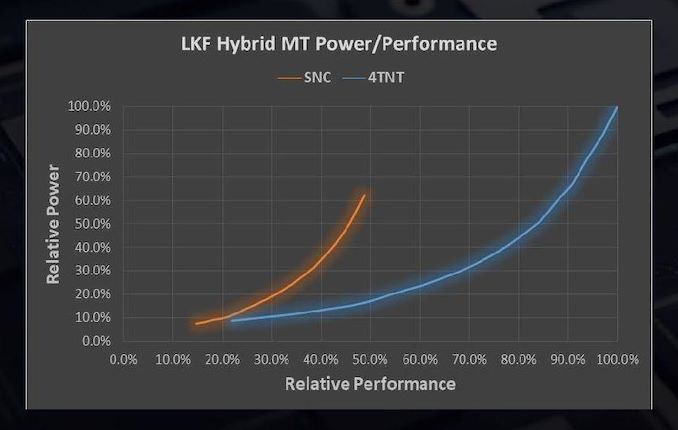

Using a similar power/performance graphs, the effect of having a 1+4 design is quite substantial. On the left is the single core power/performance graphs, but on the right is when we compare 1 Sunny Cove to all 4 Tremont cores working together.

Where the previous graph considered a 1+1 design, which is more relevant in those user experience scenarios listed above, on the right is the 1+4 design for when the user demands a heavier workload that might not be latency critical. Because there are four Atom cores, the blue line multiplies by four in both directions.

Now obviously the real world scenario is somewhere between the two, as it is possible to use only one, two, or three of the smaller cores at any given time. The CPU and the OS is expected to know this, so it can govern when workloads that can be split across multiple cores end up on either the big core or the small core.

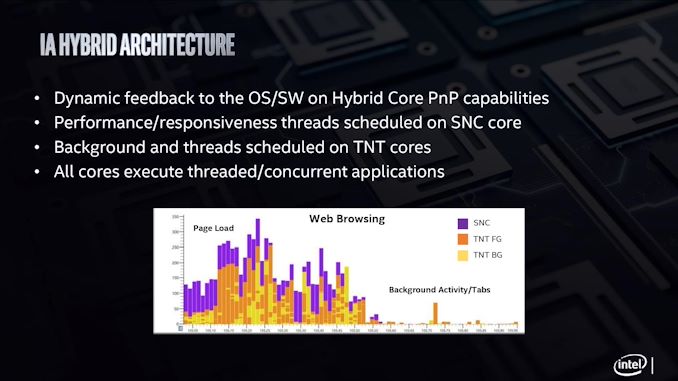

In this graph from Intel, we have three distinct modes on which threads can operate.

- ‘Sunny Cove/SNC’ is for responsiveness and user experience threads,

- ‘Tremont/TNT Foreground’, for user related tasks that require multiple threads that the user is waiting on.

- ‘Tremont/TNT Background’, for non-user related tasks run in efficiency mode

Even though the example here is web browsing, it might be best to consider something a bit beefier, like video encoding.

If we run video encoding, because it is a user related task that requires multiple threads, it will run on the four Tremont cores (TNT FG). Anything that Windows wants to do alongside that gets scheduled as TNT BG. If we then open up the start menu, because that is a responsiveness task, that gets scheduled on the SNC core.

Is 1+4 the Correct Configuration?

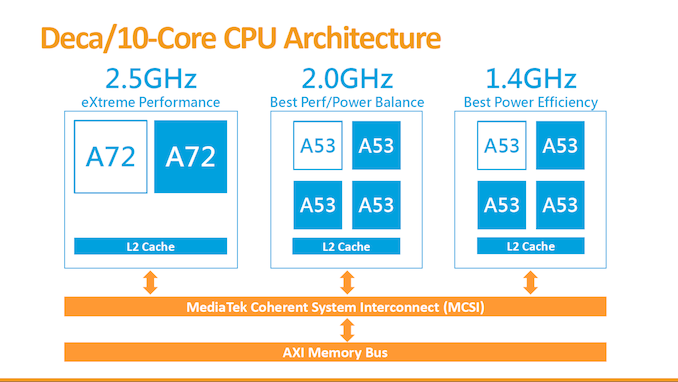

Intel here has implemented a 1+4 core design, however in the smartphone space, things are seen a little differently. The most popular configuration, by far, is a 4+4 design, simply because a lot of smartphone code is written to take advantage of multiple foreground or multiple background threads. There are a number of cost-down designs that reduce die area and power by going for a 2+4 implementation. Everyone seems adamant that 4 is a good number for the smaller cores, partly because they are small and cheap to add, but because Arm’s quad-core implementation is a base unit for its IP.

The smartphone space in recent quarters has also evolved from a two tier system of cores. In some of the more leading edge designs, we now have three types of core: a big, a middle, and a small. Because of the tendency to stay with eight core designs, we now get 1+3+4 or 2+2+4 designs, powered by complex schedulers that manage where to put the threads for the best user experience, the best battery life, or somewhere in the middle. Mediatek has been famously dabbling in 10 core designs, going for a 2+4+4 approach.

One thing missing from all of these implementations is an SoC with one big core and four small cores. Smartphone vendors don’t seem to be interested in 1+4 silicon, and yet Intel has decided on it for Lakefield. This is borne out of decisions made on both sides.

From the smartphone perspective, when hybrid designs came about, the big cores just weren’t powerful enough on their own. In order to offer something more than simply basic, at least two cores were needed, but because of how Arm architected the big and little designs, it almost became standard to look into 4+4 implementations of big and small cores. It was only until this configuration was popularized over a couple of years, and Arm big cores got more powerful, that chip designs started looking at 2+4, or 1+3+4 designs.

On Intel’s side of the fence, the biggest problem it has is the size of the Sunny Cove core. By comparison, it’s really, really big. Because the graphics core is the same as Ice Lake and reuses its design, there simply isn’t enough room within the 82 mm2 compute die to add another core. Not only that, but there is a question of power. Sunny Cove wasn’t built for sub-1W operation, even in the Tremont design. We see big smartphone silicon pulling 4-5W when all eight cores are active – there is no way, based on our understanding of Intel’s designs, that we could see four (or even two) Sunny Cove cores being in the optimal performance per watt range while being that low. Intel’s Lakefield graphics, with 64 EUs, is running at only 500 MHz – a lot lower than the Ice Lake designs. Even if Intel moved that down to a 32 EU design to make space for another Sunny Cove core, I reckon that it would eat the power budget for breakfast and then some.

Intel has made the 1+4 design to act as a 0+4 design that sometimes has access to a higher performance mode. Whereas smartphone chips are designed for all eight cores to power on for sustained periods, Lakefield is built only for 0+4 sustained workloads. And that might ultimately be its downfall. This leads onto a deep discussion about Lakefield’s performance, and what we should expect from it.

221 Comments

View All Comments

Alistair - Thursday, July 2, 2020 - link

The only point of this is if it is dirt cheap. You don't pay a premium for 1 core and 4 atom cores. DOA. I'll take a 7nm 4 core Zen 2 laptop instead thanks.Make this a $50 CPU? Then I'm interested.

lmcd - Thursday, July 2, 2020 - link

I don't think it'll be $50 but if it is, I hope to see it on single-board computers. That'd be slick.serendip - Thursday, July 2, 2020 - link

It's meant for $1000 computers, not cheap sub-$500 devices. I wouldn't pay that much money for 4 Atom cores and a big core that sits around like an unwanted appendage.lmcd - Friday, July 3, 2020 - link

It's meant for $1000 tablets and ultralights, not traditional computer form factors.Glad you won't buy any smartphone then!

yeeeeman - Friday, July 3, 2020 - link

Qualcomm is fighting in the same space with 8cx for the same huge prices and that one doesn't even run x64 apps. This market wants very light laptops with very good battery life and LKF does just that, wherever you like it or not.Spunjji - Monday, July 6, 2020 - link

We'll see what the market actually wants when this launches. I have a strong suspicion that the market doesn't want the absolutely miserable performance/$ on offer here, even for the quoted battery life benefits, but I've been wrong before.justing6 - Thursday, July 2, 2020 - link

Amazing article! I learned so much about Lakefield and 3D stacking in general. The technology and engineering is really incredible, but as a consumer product it looks extremely lacking.I'm a proud owner and heavy user of a Surface Pro X, and the 8cx/SQ1 is generally "good enough" when running ARM workloads. Going to a 15W Intel chip that can turbo to 25-40W feels noticeably snappier, but when considering the SQ1 is 7W-15W it's really impressive. The 4+4 also allows for very good multitasking performance, it takes 10GB+ of heavy web browser tabs running on an external 3440x1440p display before it really feels like it starts to slow down.

However, that's when I live inside Chromium Edge running native ARM64 code. Performance is still laughable compared to Apple Silicon, especially for translated x86 code. On Geekbench the A12z on the dev kits running translated x86 code is just as fast as the 8cx running native ARM code, while the 8cx's performance really suffers when it has to run anything more complicated than a text editor or video player written in x86. I expect Apple's successor to the A12z to mop the floor with this whole market at the same price points, even for x86 code. On top of this, Apple has unparalleled leverage over developers by controlling its entire hardware stack. I wouldn't be surprised if in 2 years, all major MacOS applications will be compiled for native ARM64 code. On the other hand, Windows on ARM64 is almost 2 years old now and has very few natively compiled apps.

I really prefer Windows, but it's going to be a hard choice for me and a lot of consumers if a Lakefield/8cx ultraportable running Windows costs the same as an Apple ultraportable on Silicon that has somewhere around double the performance for the same price, while still keeping a thin and light design with great battery life. Intel and Qualcomm will be fighting for a distant second place.

jeremyshaw - Thursday, July 2, 2020 - link

So you're saying a desktop with desktop TDP outperforms a fanless tablet with tablet TDP?I do agree Apple has a stronger push (and will have to, since they are moving their entire ecosystem over, and anyone that isn't fully onboard will simply be left behind).

Qualcomm got too greedy, Nvidia doesn't want to fight in that market anymore (remember the original Surface tablets with Nvidia Tegra chips?), and nobody else is really eyeing the laptop/consumer segment outside of Apple.

Oh, well. Some people are propping up the PINE64 as if it's worth anything.

lmcd - Thursday, July 2, 2020 - link

No one's come up with an exciting killer app beyond video decoding for smartphones or tablets so might as well "prop up" the PINE64 :)Hopefully Broadcom will get interested in SoCs again with the work they're doing with the RPi foundation. ARM is going toward powerful CPU cores anyway so it shouldn't take an Apple-sized company to come up with competitive ARM designs.

justing6 - Thursday, July 2, 2020 - link

Considering an iPad Pro (a fanless tablet) running an A12z puts up Geekbench 5 scores 30% to 60% higher that the SQ1/8cx single/multi core respectively when running native ARM code, it's safe to say its a generation or two ahead of anything Qualcomm has. I also doubt they changed much with the TDP of the chip in the Arm transition Dev kit, if anything they made it less powerful by disabling the 4 small cores and leaving it only with the 4 large cores to give them more time to work out the big.LITTLE scheduling in MacOS. A 30% hit to performance when running x86 code sounds about right, its just that the chip has so much more raw power than the 8cx that it will be able to give users a much better experience.I'm not an Apple fan by any means, but I am a fan of innovation. Apple has been pretty stagnant on that front the past decade, but with the move to ARM they have a chance to really get ahead of the market like the Apple of the 2000s.