Next Generation Intel Atom Tremont: Potential L3 Cache

by Dr. Ian Cutress on July 15, 2019 8:00 AM EST

Intel has already disclosed that it will have a next generation Atom core, code named Tremont, which is to appear in products such as the Foveros-based hybrid Lakefield, as well as Snow Ridge designed for 5G deployments. In advance of the launch of the core and the product, it is customary for some documentation and tools to be updated to prepare for it; in this case, one of those updates has disclosed that the Tremont core would contain an L3 cache – a first for one of Intel’s Atom designs.

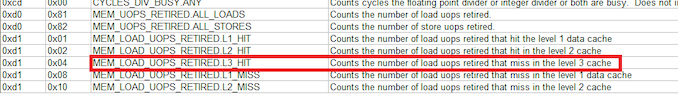

01.org is an Intel website which hosts all of its open source projects. One of those projects is perfmon, a simple performance monitoring tool that can be used by developers to direct where code may be bottlenecked by either throughput, memory latency, memory bandwidth, TLBs, port allocation, or cache hits/misses. In this case, the profiles for Snow Ridge have been uploaded to the platform, and one of the counters provided includes provisions for L3 cache monitoring. This provision is directly listed under the Tremont heading.

Enabling an L3 cache on Atom does two potential things to Intel’s design: it adds power, but also adds performance. By having an L3, it means that data in the L3 is quicker to access than it would be in memory, however there is an idle power hit by having L3 present. Intel can mitigate this by enabling parts of the L3 to be powered on as needed, but there is always a tradeoff. There can also be a hit to die area, so it will be interesting to see how Intel has changed the microarchitecture of it’s Atom design. There is also no indication if the Tremont L3 cache is an inclusive cache, or a non-inclusive cache, or if it can be pre-fetched into, or if it is shared between cores or done on a per-core basis.

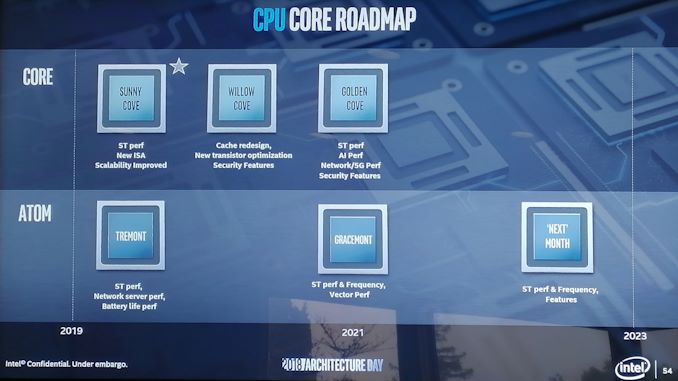

Intel’s Atom roadmap, as disclosed last year at Architecture day, shows that the company is planning several more generations of Atom core, although beyond Tremont we get Gracemont in 2021, and beyond that is ‘increased ST Perf, Frequency, Features’ listed around 2023. In that time, Intel expects to launch Sunny Cove, Willow Cove, and Golden Cove on the Core side.

The first public device with Tremont inside is expected to be the Core/Atom hybrid Lakefield processor, which uses Intel’s new Foveros stacking technology. We know that this design will have one Sunny Cove core and pair it with four Tremont cores. Intel expects chip production of Lakefield for consumer use by the end of the year.

Related Reading

- Intel's Architecture Day 2018: The Future of Core, Intel GPUs, 10nm, and Hybrid x86

- Intel Lists New Atom Core: Tremont to Come After Goldmont Plus

- Intel’s Keynote at CES 2019: 10nm, Ice Lake, Lakefield, Snow Ridge, Cascade Lake

- Intel's Interconnected Future: Combining Chiplets, EMIB, and Foveros

Source: InstLatX64, 01.org

66 Comments

View All Comments

mode_13h - Wednesday, July 17, 2019 - link

Lol... architexture... sounds like some GPU rendering hack, but actually found a site by that name that seems to sell texture maps for buildings. Makes sense...Maybe he was listening to this: https://en.wikipedia.org/wiki/Architextures

Lord of the Bored - Tuesday, July 16, 2019 - link

I stand corrected. 'S what I get for ignoring the pictures.You're right, NextMont wouldn't be bad at all.

nobodyblog - Friday, July 19, 2019 - link

Apple's SOC is faster only for 30 seconds. Then expect almost %50 drop in speed.mode_13h - Monday, July 22, 2019 - link

Presumably, you're referring to the iPad, which has limited cooling capacity. Expect to see better sustained performance in a larger device, like a laptop.