Original Link: https://www.anandtech.com/show/13774/intels-keynote-at-ces-2019-10nm-ice-lake-lakefield-snow-ridge-cascade-lake

Intel’s Keynote at CES 2019: 10nm, Ice Lake, Lakefield, Snow Ridge, Cascade Lake

by Ian Cutress on January 7, 2019 7:45 PM EST

This year it seems that Intel is finally ready to talk about 10nm. After next-to-nothing on the subject at CES 2018, Intel is now talking about three new processor families: Ice Lake, Lakefield, and Snow Ridge. Despite the naming, it looks like Intel might be coming in out of the cold – to finally let it go – and roadmaps on upcoming products are being discussed.

It should be pointed out that Intel’s presentation did not mention anything about the company’s search for a new CEO, or any updates about Intel’s increased demand for its high-end Xeon processors. These are matters that the company will no doubt want to save for their earnings release later this month.

Stage 1: Consumer

Intel Client Group SVP Gregory Bryant took to the stage for Intel to announce two major hardware platforms and a new initiative in mobile computing. These were Ice Lake, Lakefield, and Project Athena.

Ice Lake: First Volume 10nm

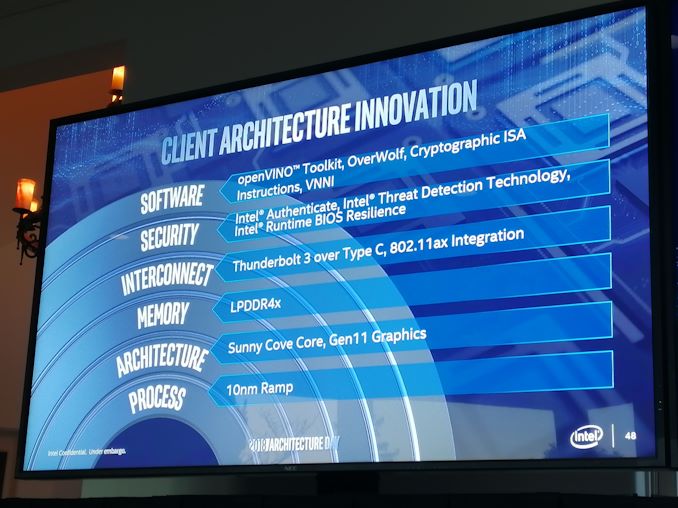

One of the topics discussed at Intel’s Architecture Day, but under embargo until this week, is Intel’s vision for its first generation of 10nm-class consumer processors. We had already been given some details about Sunny Cove, the new Core design, as well as the updated Gen11 graphics architecture, but it will be Ice Lake that puts them both together.

Ice Lake, or more specifically Ice Lake-U it would appear, will be Intel’s first volume client processor on 10nm. Mobile processors are usually small, so it makes sense for Intel to use one for their first volume part in order to balance yields and costs – we’ve seen it before with 14nm, where Broadwell-U entered the market first. The base design from Intel looks to have four cores, eight threads, and 64 GPU execution units for graphics. Intel stated that they are driving the die area even more towards graphics under Gen11 in order to get more performance. This will be, according to Intel, its first standard (GT2-class) processor with 1 TFLOP of integrated graphics performance.

| Intel Ice Lake '4+2' For Notebooks | |

| Manufacturing Process | Intel 10nm |

| Cores / Threads | 4 / 8 |

| CPU Microarchitecture | Sunny Cove |

| Graphics Microarchitecture | Gen11 |

| Graphics Execution Units | GT2, 64 |

| TDP | 15W |

| Memory | LPDDR4X - yes LPDDR4X-3200 ? |

| Memory Bandwidth | 50-60 GB/s |

| Connectivity | TB3 over Type-C Wi-Fi 6 (802.11ax) with CRF |

| Image Processing Unit | 4th Gen |

Hardware wise, Intel explained that these processors would be using LPDDR4X. In a different segment of the presentation it was mentioned that the increase in integrated graphics (from a 24 EU configuration to a 64 EU configuration) required increasing memory bandwidth up to at least 50 GB/s. Intel did not disclose the specific memory frequencies supported, but with these bits of information I’d put LPDDR4X-3200 as the lower bound, as it offers 51.2 GB/s of bandwidth in dual channel mode. This is surprising, given that Intel is usually conservative with supported memory speed declarations – they still make a DDR4-2933 processor in their lineup – so jumping to 3200 would indeed be an unexpected shift for the company.

On the connectivity side, the chipsets for Ice Lake will enable Wi-Fi 6 (802.11ax) over the CNVi interface when an appropriate Intel CRF module is installed. Native Thunderbolt 3 is also expected, which of course operates over USB Type-C connections. Intel reworked the interface for camera support as well, adjusting the interface such that a MIPI-to-USB chip is no longer needed in a laptop bezel for webcam support.

Intel also mentioned software support, such as the new VNNI instructions, openVINO toolkit support, Cryptographic ISA instructions, and support for Overworld. These processors will have at least a similar security level as Cascade Lake, with hardware-enabled Spectre v2 mitigations.

Intel's Image Processing Unit, or IPU, is also upgraded to a fourth generation model. This part of the chip, according to Intel, now has a concurrent imaging pipeline for machine learning, and can support a single IR/RGB camera for login (e.g. Windows Hello). The IPU's power plane has also been tweaked, giving it more performance/power states so the system can save power as needed.

Ice Lake Designs: More Battery Life

Beyond the 10nm process node change, Intel also announced two additional ways in which it was improving battery life for Ice Lake-U systems. Firstly, the company described its efforts on platform innovation, saying they did a top-to-bottom analysis of what in the system is drawing power and finding ways to reduce it while still keeping performance. As a result, combined with the new ‘1W’ display technologies the company introduced at Computex in June, we’ve been told that optimized Intel devices should now be able to achieve 25+ hours of battery life.

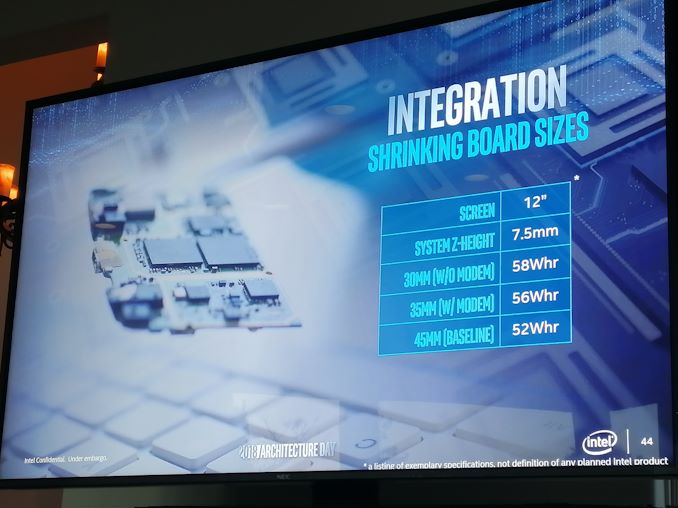

Following a similar line of reasoning, Intel also reworked the board design specifications for thin and light devices. For a typical 12-inch laptop, Intel has freed up room for about 10% more battery capacity – going from 52 Wh to 58 Wh – thanks to reducing the total z-height and x/y dimensions of the motherboard. Interestingly, they've accomplished this without reducing the component count, bringing down the board size while retaining a given number of components.

Lakefield: Foveros Technology Coming Soon

At Intel’s Architecture Day in December, we saw a new class of chip from the company: a hybrid x86 CPU. It was a big announcement for two reasons: the first was that it featured both Core architecture and Atom architecture CPU cores, something that Intel had never done before. Ever since Arm's success with the similar concept of big.Little designs, we have been expecting Intel to come out with some products following this idea, but it was big news that this was finally the time. The second reason for it being a big announcement is that it used ‘Foveros’, Intel’s 3D active interposer technology that puts the cores and graphics on a chip on an interposer. However in a wrinkle from other interposer-based solutions, Foveros but puts the IO in the interposer (rather than using the interposer as a 'dumb' piece of silicon to route signals) all with through-silicon vias to make it work. A chip like this is much smaller in the x/y dimensions, as well as showcasing some very nice packaging technology.

Intel is giving that chip an official family name: Lakefield. The goal of designing Lakefield came from an OEM request to develop a chip that had 2 mW idle power draw, something much lower than current designs. Thus Lakefield was created. It uses a single Sunny Cove core, four Tremont Atom cores, and Gen11 graphics, all built on 10nm.

There have been questions about where exactly this chip will end up, or who even asked for it in the first place. Intel has stated that while a single customer put in the request, Lakefield will be available to all OEM partners if they want to design products around it. A lot of discussion has been held that this was an Apple request, and given Apple’s device portfolio, its volume of sales, and its desire to drive down power with optimized unique designs, the argument for Apple holds some water. But it doesn't sit right with me. This is more a low-powered chip, perhaps even lower power than the A12X in the iPads, so I don’t think Apple would want that chip in one of its MacBooks. (When we asked at architecture day, they said the chip could easily compete at the 7W TDP range, but I imagine it could go lower if needed.) Personally I’m of the opinion that it’s for the dual-screen Lenovo Yogabook. That device is super thin, super light, powers an LCD display and an eInk-like display, and doesn’t need that much power to do what it needs to do. But because it’s so thin there's limited room for battery cells, meaning that power consumption and the resulting battery life are all important, which is where Lakefield is likely to excel.

Intel announced that Lakefield was expected to be in production for products in 2019, which aligns with Intel’s commitment to having 10nm devices on shelves for the holiday season in 2019 (which would mean Christmas 2019).

Project Athena: Building Devices Ready for AI and 5G

As the single biggest force behind the PC ecosystem – and yet not a company that's selling hardware directly to consumers in most cases – Intel enjoys creating programs that try and push the market in certain directions. Depending on who you talk to, the Ultrabook program was either a big failure or a big success, but in the end it did give OEMs a chance to play with thin and light designs for a few years before the hardware gave users a good user experience and battery life. Project Athena is something slightly different, in that it will be a program for Intel and OEMs to work together to enable new experiences with technology coming in the next decade.

Terms like ‘5G’ and ‘Artificial Intelligence’ are only going to become more ubiquitous through 2020 and beyond, so Intel is jumping on it today. Current connectivity experiences for notebooks and laptops vary significantly, and AI implementations are either basic or removed from the local machine entirely and processed in cloud servers. With Project Athena, Intel is going to discuss with OEMs, with partners, customers, software developers, etc. what they need in order to enable these new terms to provide a good user experience. It isn’t just limited to 5G and AI, but we might see more requests for better AI toolkits, or power optimized designs for mobile connectivity, or more compute-related acceleration. It also extends to OEMs in their device design – if an OEM needs several cameras, or new biometrics, or supports more gestures, or new microphone array capabilities etc.

As this is a new program based in aspirational discussion followed by execution, it is unclear what the end goal will look like, only that the aim is around improvements to user experiences.

New 9th Gen Core CPUs

Intel also announced, briefly, that they will be releasing six new desktop 9th Gen Core processors, from Core i3 to Core i9. It did not disclose which parts or what the specifciations are, however we assume they will be available soon. We found the parts listed on Intel's ARK database just after the keynote and you can read our writeup here.

Also in the 9th Gen space, Intel said that the mobile 9th Gen Core processors will be available in Q2.

Stage 2: Datacenter

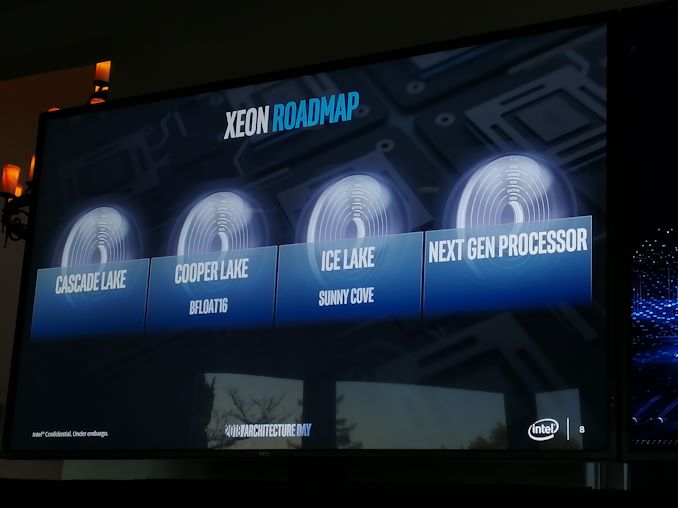

Intel’s Datacenter Group SVP, Navin Shenoy, also took to the stage at CES in order to discuss some new products in Intel’s portfolio, as well as to deliver updates on ones that were disclosed last year. Back in 2018, Intel held its Datacenter Summit in August, where it lifted the lid on Cascade Lake, Cooper Lake, and 10nm Ice Lake. Along with this, we saw new instruction support for AI and security as the top two areas of discussion.

Cascade Lake: Get Yours Today

Intel’s first generation of Xeon Scalable processors, Skylake-SP, was launched over 18 months ago. We’ve been hearing about the update to that family, Cascade Lake-SP, for a while now, along with its brother Cascade Lake-AP and how it will tackle the market. The announcement today from Intel is that the company is now shipping Cascade Lake for revenue.

This means, to be crystal clear, that select customers are now purchasing production-quality processors. What this doesn’t mean is retail availability. These select customers are part of Intel’s early sampling program, and have likely been working with engineering samples for several months. These customers are likely the big cloud providers, the AWS / Google / Azure / Baidus of the world.

It’s worth pointing out that at Intel’s Datacenter Summit, they said that half of all of its Xeons sold were ‘custom’ processor configurations that were not sold though its distributors – these parts are often described as ‘off roadmap’. It is likely that when Intel says Cascade Lake-SP is shipping for revenue to select customers that they are likely to be purchasing these off-roadmap processors. They might be running at a higher TDP than Intel expects for the commercial parts, or have different core/cache/frequency/memory configurations as and when they are needed.

One of the big draws for Cascade Lake is Intel’s Optane DC Persistent Memory support, which will enable several terabytes of memory per socket, but also the hardware security patches for Spectre v2. Businesses who want to be sure their hardware is patched can guarantee security if it's in the hardware, rather than relying on a firmware/software stack. So this might be part of why Intel’s demand for 14nm CPUs is at an all-time high and outstripping supply – if a company wants to be 100% sure it is protected, they need the hardware with baked-in security.

The full retail launch of Cascade Lake is expected in 2019. Based on what we saw at Supercomputing in November, given by a rolling slide deck at the booth of one of Intel’s OEM partners, that time frame looks to be somewhere from March to May.

Nervana for Inference: NNP-I coming in 2019

To date, when Intel has discussed the Nervana family of processors, we have only known about them in the context of large-scale neural network acceleration. The idea is that these big pieces of silicon are designed to accelerate the types of compute commonly found in neural network training, at performance and power efficiency levels above and beyond what CPUs and GPUs can do. It has been disclosed that Intel is working on that family of parts, NNP-L, for a while now, and we are still waiting on a formal launch. But in the meantime, Intel is announcing today that it is working on a part that's optimized for inference as well.

There are two parts to implementing machine learning with neural networks: making the network learn (training), and then using the trained network on new information to do its job (inference). The algorithms are often designed such that the more you can train a network, the more accurate it is and sometimes the less computationally intensive it is to apply it to an external problem. The more resources you put into training, the better. But the scale of compute between training and inference is several orders of magnitude: you need a big processor for training, but don’t need a big processor for inference. This is where Intel’s announcement comes in.

The NNP-I is set to be a smaller version of the NNP-L and built specifically for inference, with Intel stating that it will be coming in 2019. Exact details are not being disclosed at this time, so we don't have any information on the interface (likely PCIe), power consumption, die size, architecture, etc. However, we can draw some parallels from Intel’s competition. NVIDIA has big Tesla V100 GPUs with HBM2 for training that can draw 300-350W each, with up to eight of them in a system at once. However for inference it has the Tesla P4, which is a small chip below 75W, and we’ve seen systems designed to hold 20 of NVIDIA's various inference processors at once. It is likely that this new NNP-I design is along the same lines.

Snow Ridge on 10nm: An SoC for Networking and 5G (Next-Gen Xeon-D?)

The Data Center Group will be making two specific announcements around 10nm. The first is disclosing the Snow Ridge family of processors, focused on networking and specifically targeting the wide array of 5G deployments coming up over the next decade. The purpose of Snow Ridge is to enable wireless access base stations and deployments, as well as functions required at the edge of the network, such as compute, virtualization, and potentially things like artificial intelligence.

Intel gave no other details, however going back in my mind, I realise that we’ve heard this before with Intel. They already have processors on their roadmap focused specifically on networking, with 40 GbE support and features like QuickAssist Technology to accelerate networking cryptography: the Xeon-D line of processors. This makes me believe that Snow Ridge will be the name for the next generation of Xeon D, either the Xeon D-2500 or Xeon D-3100, depending on the power envelope Intel is going for.

Given this assumption, and the fact that Intel has said that this is a 10nm processor, I suspect we’re looking at a multi-core Sunny Cove enterprise design with integrated networking MACs and support for lots of storage and lots of ECC memory. There’s an outside chance that it might support Optane, allowing for bigger memory deployments, although I wouldn’t put money on it at this stage.

Ice Lake Xeon Scalable on 10nm

To finish up Intel’s announcements, Nevin also talked about Ice Lake Xeon Scalable. At Intel’s Architecture Day, a processor was shown at the event that was described as Ice Lake Xeon, so this is just Intel repeating the fact that they now have working silicon in the labs. There is still no word as to how Intel is progressing here, with question marks over the yields of the smaller dies, let alone the larger Xeon ones. Working silicon in this case is just a functional test to make sure it works – what comes now is the tuning for frequency, power, performance, and optimizing the silicon layout to get all three. I’m hoping that Intel keeps us apprised of its progress here.

What Happened at CES 2018, and why CES 2019 is Different

A memory that will stick in my mind is Intel’s CES 2018 announcements. At the heart of the show, we wanted to know about the state of Intel’s 10nm process, and details were not readily available. 10nm wasn’t mentioned in the keynote, and when I tried to ask then-CEO Brian Krzanich about it, another Intel employee hastily cut in to the conversation saying that nothing more would be said. In the end we got a single sentence from Gregory Bryant at an early morning presentation the day after the keynote, and that sentence was only after 10 minutes of saying how well Intel was executing. That single sentence was to say that Intel was shipping 10nm parts in 2017, although so far only two consumer products (in limited quantities, and region specific) have ever been seen.

This year, coming off the back of Intel’s Architecture Day last month, shows that Intel is becoming more open to discussing future products and roadmaps. A lot of us in the press and analyst community are actively encouraging this trend to continue, and the contrast between CES 2018 and CES 2019 is clear to see. Companies tend to hide or obfuscate details when product execution isn’t going to plan; now that Intel is starting to open up with details, the outlook is clearly returning to one with more optimism.