AMD: “No Chiplet APU Variant on Matisse, CPU TDP Range same as Ryzen-2000”

by Ian Cutress on January 11, 2019 12:30 PM EST- Posted in

- CPUs

- AMD

- Trade Shows

- Zen 2

- CES 2019

- Ryzen 3rd Gen

- Matisse

One of the big questions coming out of AMD’s CES announcements was if its new CPU design, codenamed Matisse and which enables two chiplets and an IO die on a single package, would support one of those chiplets being graphics based in order to make an APU. In our discussions with AMD, we received confirmation that this will not be the case.

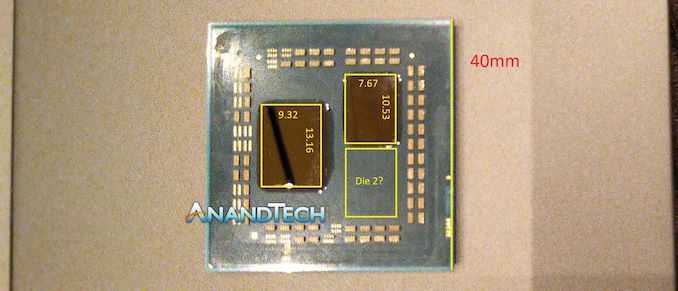

The new Matisse design is the platform for AMD’s next generation of desktop processors. The layout shown at CES this year represented the design as having a single IO die, about 122.6 mm2 and built on GlobalFoundries 14nm, paired with a chiplet die, about 80.8 mm2, containing eight cores and built on TSMC’s 7nm. There is obviously space on that package for another CPU chiplet, and there has always been questions if the chiplet design is amenable to using a graphics chiplet instead.

AMD stated that, at this time, there will be no version of the current Matisse chiplet layout where one of those chiplets will be graphics. We were told that there will be Zen 2 processors with integrated graphics, presumably coming out much later after the desktop processors, but built in a different design. Ultimately APUs are both mobile first as well as lower cost parts (usually), so different design decisions will have to be made in order to support that market.

This doesn't rule out a future processor using chiplet graphics, this is just for Matisse.

Our contacts at AMD also discussed the TDP range of the upcoming range of Matisse processors. Given AMD’s definition of TDP, relating to the cooling performance required of the CPU cooler, the range of TDPs for Matisse will be the same as current Ryzen 2000-series processors. This means we could see ‘E’ variants as low as 35W TDP, all the way up to the top ‘X’ processors at 105W, similar to the current Ryzen 7 2700X. We were told that the company expects the processors will fit within that range. This should be expected on some level, given the backwards compatibility with current AM4 motherboards on the market with a BIOS update.

Read our announcement on the early preview of the Matisse processors here:

https://www.anandtech.com/show/13829/amd-ryzen-3rd-generation-zen-2-pcie-4-eight-core

52 Comments

View All Comments

Cooe - Friday, January 11, 2019 - link

Already have. Just like all 14nm Zen Raven Ridge SKUs were under the 2000 series umbrella, all 12nm Zen+ Picasso parts will have 3000 series model numbers (i.e. expect a 3200G & 3400G on desktop). See the just launched 2nd Gen Ryzen Mobile SKUs (using Picasso) for an example.Teckk - Saturday, January 12, 2019 - link

Cool, thanks for clarifying. Not consistent but that's how they're doing it every time then. 👍nemi2 - Friday, January 11, 2019 - link

Please let there be an option for the 2nd chiplet to be a massive amount of level 3/4 cache...PeachNCream - Friday, January 11, 2019 - link

Cache size increases experience diminished returns so an absurdly large SRAM cache, while admittedly cool on paper, may not justify the cost increase with greater performance. Also the off-die nature of a chiplet being used as a cache pool would likely further reduce cache benefits by adding distance and communication related latency. The nerdy side of me is cheering for HBM, but that Mattise IC package doesn't look like an interposer which, as far as I know, is mandatory for current HBM implementations. That leaves DRAM or some eDRAM/Crystalwell-like animal. DRAM might not like sharing the same IHS and HSF as the rest of the CPU package though it would be a potential competitor for that real estate given the locality of the IO die with its memory controllers. The temperatures DRAM would experience could be detrimental to performance and eDRAM was an Intel thing that offered about 50GB/s which is what DDR4 in dual-channel is now delivering albeit at higher latency.Santoval - Friday, January 11, 2019 - link

"The nerdy side of me is cheering for HBM, but that Mattise IC package doesn't look like an interposer which, as far as I know, is mandatory for current HBM implementations."An interposer is not "mandatory" for HBM. If it was mandatory Kaby Lake-G could not have had its HBM stack connected to the GPU via EMIB. Now, EMIB is quite faster than IF so it would have a bandwidth and latency advantage, at the trade-off of being very close range. Yet I don't see why IF could not be used for HBM.

Spunjji - Monday, January 14, 2019 - link

EMIB is an Intel technology, for the time being at least. I very much doubt we'll see it on an AMD CPU any time soon.CajunArson - Friday, January 11, 2019 - link

While a 16 core RyZen 2 that for whatever reason AMD couldn't get running for CES will make the fanboys happy (even though they already have Thread rippers... Right?) it's a flat out dumb idea to leave a giant swath of the market that uses integrated graphics for basically everything that's not a AAA game unaddressed.You'll also not that AMD used to love to mention Navi at it's talks. Funny how it disappeared at CES. Connection?

ArcadeEngineer - Friday, January 11, 2019 - link

Given the Radeon VII announcement lack of Navi mention doesn't require additional explanation. They aren't going go 'here's our fancy new GPU, and here's the one that will make it obsolete in six months'.StevoLincolnite - Friday, January 11, 2019 - link

Navi is likely a Polaris replacement, not a Vega replacement.Dragonstongue - Saturday, January 12, 2019 - link

Navi is NOT a desktop card replacement, this has been known about for a few months, the name itself was unknown, Radeon VII (seven, or five too when spoken) was not known before CES and the replacement for Vega was known to becoming, so the V in the name, second gen of VG, makes sense to me.If AMD CPU teams took the ideas to heart of what they did going from Athlon 64 coming forward to Bulldozer leading to Ryzen truly to heart, to keep the ball rolling, they will be doing exceptional in a couple of years time...

If I had $10-150k to plunk down on them today (could afford it) I would, but I cannot :( T_T

On the GU side of the equation, they went from the Radeon 1900 series to the 2k forward to 7k and you can tell that their funding went quite down hill as although there were some "beast" cards they lost that sweet spot middle that they established a few years prior in the 4k series (4870 was the top...5k 5970 was top level enthusiast but 5870 had very decent performance, 6870 was "close" could overclock a touch to match the 5870 for less power, 6970 was a "new" VLIW approach, n using 4 medium fat process everything shaders, instead of 1 fat process all and 4 process specific tasks in a more threaded fashion toe the meaning hundreds of dispatchers..

Anyways, ahead we come to polaris, which effectively uses a modernized combination or fusion of VLIW-4 and VLIW-5 at GCN7 (I believe for Vega II, for GCN version as well) Polaris is level 6 (Vega is as well)

Polaris was the "top" for gaming grade but the enthusiast branding "morphed" a few times over their years offering highest performance for the workstation offerings and so it did with the desktop grade as well not being known "simply" by the highest model number but also like Nano/Fury, and it seems like now the Vega will be the "top" and become its own "chain" opr at least should IMHO such as best cutting edge VR grunt etc and the more "main stream" like the 7870 many years ago will be the new NAVI when it releases.

To establish two lines for their long term ideas would not kill them, it might actually help them focus their "assembly line" for ideas.

I get mainstream, I budget, I get mobile, I get high end, I get enthusiast, workstation, enterprise, server,

Titan is a "good example" of workstation grade, IMO this is where AMD has done will over the years with dual-gpu on one card (often times better then Nv did) then they also did with the 90 versions or the X numbers just being a high shader/clock card type thing, Vega in its own right is a "titan" for desktop use, and the x70 and x80 naming they now seem to use will become the "Navi" using numbers in its name.

I do not see them doing much cut down versions of Radeon VII otherwise it would just be a Vega 64, and if "true" they only have another 4 CU to go before it reaches GCN design limits of 4096 or was 4560 or something like that shader count?